Your **definitive** source for quality pre-owned equipment.

## **Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

#### Full-service, independent repair center

with experienced engineers and technicians on staff.

We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins.

#### **Custom engineering**

so your equipment works exactly as you specify.

- Critical and expedited services

- Leasing / Rentals / Demos

In stock / Ready-to-ship

• ITAR-certified secure asset solutions

Expert team | Trust guarantee | 100% satisfaction

All trademarks, brand names, and brands appearing herein are the property of their respective owners.

Find the Interphase V/Ethernet 4221-1PT-AUI/UPT-128 at our website: Click HERE

# V/Ethernet 4221 Condor User's Guide

Document No. UG04221-000, REVB Release date: July 1994

> Copyright 1994 Interphase Corporation All Rights Reserved

## **Copyright Notice**

Copyright 1993, 1994 by Interphase Corporation All rights reserved

No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including, but not limited to photocopy, photograph, electronic, or mechanical, without prior written permission of:

## **Interphase Corporation**

13800 Senlac Dallas, Texas 75234 Phone: (214) 919-9000 FAX: (214) 919-9200

## **Disclaimer**

Information in this user document supercedes any preliminary specification, data sheets, and/or any other documents that may have been made available. Every effort has been made to supply accurate and complete information. However, Interphase Corporation assumes no responsibility or liability for its use. In addition, Interphase Corporation reserves the right to make product improvement without prior notice. Such improvements may include, but not limited to, command codes and error codes.

## For Assistance

To place an order for an Interphase product, call:

Sales Support: (214) 919-9000

For assistance using this, or any other Interphase product, call:

Customer Service: (214) 919-9000 United Kingdom: +44-869-321222

To send in a board for repair or upgrade, call:

RMA Coordinator: (214) 919-9000

## **Trademark Acknowledgments**

All terms used in this manual that are known to be trademarks or service marks are listed below. In addition, terms suspected of being trademarks have been appropriately capitalized. Use of a term in this manual should not be regarded as affecting the validity of any trademark or service mark.

- Interphase is a registered trademark of Interphase Corporation.

- Virtual Buffer Architecture<sup>SM</sup>, BUSpacket Interface<sup>SM</sup>, and CacheFlow<sup>SM</sup> are service marks of Interphase Corporation.

- UNIX® is a registered trademark of AT&T Bell Laboratories.

- IBM® is a registered trademark of International Business Machines.

- 80486® 82503®, and 82596A® are registered trademarks/product marks of Intel.

- MC68EC030® and MC68040® are registered trademarks/product marks of Motorola.

# TABLE OF CONTENTS

| CHAPTER 1                                          |

|----------------------------------------------------|

| INTRODUCTION                                       |

| Intended Audience                                  |

| Scope Of Manual                                    |

| References                                         |

| Conventions                                        |

| General Description                                |

| Features                                           |

| Options                                            |

| Physical Description                               |

| Functional Description                             |

| Ethernet Front End Channel (FEC)                   |

| VMEbus Master Interface                            |

| DMA Engine                                         |

| VMEbus Drivers And Receivers                       |

| Local Bus                                          |

| VMEbus Short I/O Interface                         |

|                                                    |

| CPU Core                                           |

| CPU/LBUS Interface                                 |

|                                                    |

| CHAPTER 2                                          |

| HARDWARE INSTALLATION                              |

| Overview                                           |

| 4221 Condor Hardware Installation Procedures       |

| Step 1. Visual Inspection                          |

| Step 2. Fuse And Diagnostic LEDs                   |

| Step 3. Set Onboard Motherboard Jumpers            |

| Step 4. Set Daughter Card Jumpers And Terminations |

| Step 5. Power Off System                           |

| Step 6. Cabling Procedure                          |

|                                                    |

| CHAPTER 3                                          |

| MACSI HOST INTERFACE                               |

| Introduction                                       |

| Typographic Convention                             |

| Memory Address                                     |

| Field Offset                                       |

| Contiguous Data Allocation                         |

| System Interface                                   |

| MACSI Organization                                 |

| Master Control Status Block (MCSB)                 |

| Master Status Register (MSR)                       |

| Master Control Register (MCR)                      |

| Onboard Command Queue Entry                        |

| Queue Entry Control Register (QECR)                |

| IOPB Address                                       |

| Command Tag                                        |

| Work Queue Number. 60                              |

| Offboard Command Queue Entry                       |

| Queue Entry Control Register (QECR)                |

|                                                    |

| DMA Transfer Control Word                          |

| DMA Transfer Control Word                          |

| Host Address                                       |

|                                                    |

| Command Response Block (CRB)                  | . 62 |

|-----------------------------------------------|------|

| Command Response Status Word (CRSW)           | . 62 |

| Command Tag                                   | . 63 |

| IOPB Length                                   | . 63 |

| Work Queue Number                             | . 63 |

| Multiple Completed Returned IOPB Structure    | . 64 |

| Command Tag                                   | . 64 |

| Port                                          | . 64 |

| Work Queue Number                             | . 64 |

| Transfer Count                                | . 64 |

| Configuration Status Block (CSB)              | . 65 |

| Product Code                                  | . 65 |

| Product Variation                             | . 65 |

| Firmware Revision Level                       | . 66 |

| Firmware Revision Date                        | . 66 |

| Ethernet MAC Addresses (Ports 0 - 3)          | . 66 |

| Controller Statistics Block                   |      |

| Transmit Commands Submitted                   |      |

| Transmit DMA Completions                      |      |

| Transmit 82596 Completions                    |      |

| Successful Transmits                          |      |

| Failed Transmits                              |      |

| Transmit Completions Posted to Host           |      |

| Receive Commands Submitted                    |      |

| Receives Dropped - No Pending Receive Command |      |

| Receive 82596 Completions                     |      |

| Failed Receives                               |      |

| Receive DMA Completions                       | . 69 |

| Receive Completions Posted to Host            |      |

| IO Parameter Blocks (IOPBs)                   |      |

| Common IOPB Structures                        |      |

| Command Code                                  | . 71 |

| Command Options                               |      |

| Return Status.                                |      |

| Normal Completion Level / Vector              | . 71 |

| Error Completion Level / Vector               |      |

| DMA Transfer Control Word                     |      |

| Initialize Controller                         | . 73 |

| Command Code                                  | . 73 |

| Controller Initialization Block Offset        | . 73 |

| Controller Initialization Block (CIB)         | . 74 |

| Number of CQE Entries                         | . 74 |

| Special Network Options                       | . 75 |

| Ethernet Physical Node Addresses              | . 75 |

| Interrupt Levels and Vectors                  | . 75 |

| DMA Burst Count                               | . 75 |

| Offboard CRB DMA Transfer Control Word        | . 76 |

| Offboard CRB host address                     | . 76 |

| MAC Control/Status                            | . 77 |

| Command Code                                  | . 78 |

| Command Options                               | . 79 |

| Return Status                                 | . 80 |

| Buffer address                                | . 80 |

| Transfer size                                 | . 80 |

| MAC status/control                                                                              |      |

|-------------------------------------------------------------------------------------------------|------|

| Intel 82596 Status/Control – Transmit Functions  Intel 82596 Status/Control – Receive Functions |      |

|                                                                                                 |      |

| MAC returned information                                                                        |      |

| Change Default Node Address.                                                                    |      |

| Command Code                                                                                    |      |

| Command Options                                                                                 |      |

| Transmit                                                                                        |      |

| Command Code                                                                                    | . 87 |

| Command Options                                                                                 | . 88 |

| Transmit In-Line Gathers                                                                        | . 88 |

| Number of Elements                                                                              | . 89 |

| Total transfer count                                                                            | . 89 |

| Element transfer count                                                                          |      |

| Buffer address                                                                                  |      |

| Receive                                                                                         |      |

| Command Code                                                                                    |      |

| Command Options.                                                                                |      |

| Buffer Address.                                                                                 |      |

| Maximum / Actual Transfer Size                                                                  |      |

|                                                                                                 |      |

| Packet Type / Length Field                                                                      |      |

| Source Address                                                                                  |      |

| Initialize Multiple Completions                                                                 |      |

| Command Code                                                                                    |      |

| Command Options                                                                                 |      |

| Return Status                                                                                   |      |

| Control Flags                                                                                   |      |

| Group Interrupt Level / Vector                                                                  |      |

| Minimum Group Count                                                                             |      |

| Maximum Group Count                                                                             |      |

| Report Network Statistics                                                                       | . 95 |

| Command Code                                                                                    |      |

| Command Options                                                                                 | . 96 |

| Return Status                                                                                   | . 96 |

| Host Memory Buffer Address                                                                      | . 96 |

| Max Transfer Size                                                                               | . 96 |

| Timer Interval                                                                                  | . 96 |

| Network Statistics Block                                                                        | . 97 |

| Data Valid Indicator                                                                            | . 97 |

| Port Indicator                                                                                  |      |

| Transmits Submitted                                                                             |      |

| Transmits Completed.                                                                            |      |

| Transmits Failed                                                                                |      |

| Collisions                                                                                      |      |

| Receives Submitted                                                                              |      |

| Receives Returned                                                                               |      |

| Receives Dropped (Resources)                                                                    |      |

| Receives Dropped (Resources)                                                                    |      |

| Received Diopped (Elitois)                                                                      | . 70 |

| APPENDIX A                                                                                      |      |

| SPECIFICATIONS                                                                                  | ga   |

| VMEbus Specifications                                                                           |      |

| Power Requirements                                                                              |      |

| Mechanical (Nominal)                                                                            |      |

| 1420-1411-141 (1.10-1111-141)                                                                   | 100  |

| Operating Environment           | 100 |

|---------------------------------|-----|

| Fuse                            | 100 |

| Reliability                     | 100 |

| APPENDIX B                      |     |

| CONNECTOR PINOUTS AND CABLING   |     |

| Overview                        |     |

| VMEbus Connectors               | 102 |

| Ethernet Connectors and Pinouts | 104 |

| RS232 Connector and Cable       | 106 |

| APPENDIX C                      |     |

| ERROR CODES                     | 107 |

# LIST OF FIGURES

| Figure 1-1. | 4221 Condor Block Diagram                                       | <br>. 3 |

|-------------|-----------------------------------------------------------------|---------|

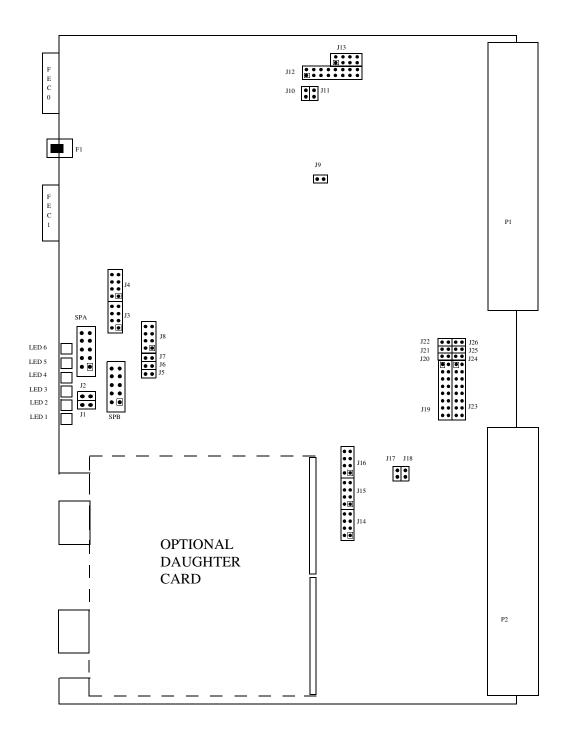

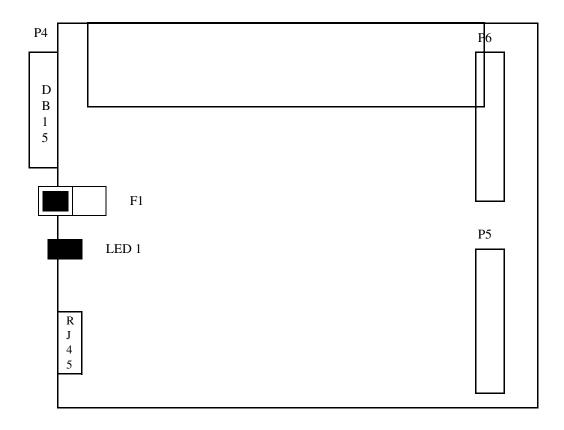

| Figure 2-1. | 10BaseT Condor Motherboard Layout (PB04221-000)                 | <br>. 9 |

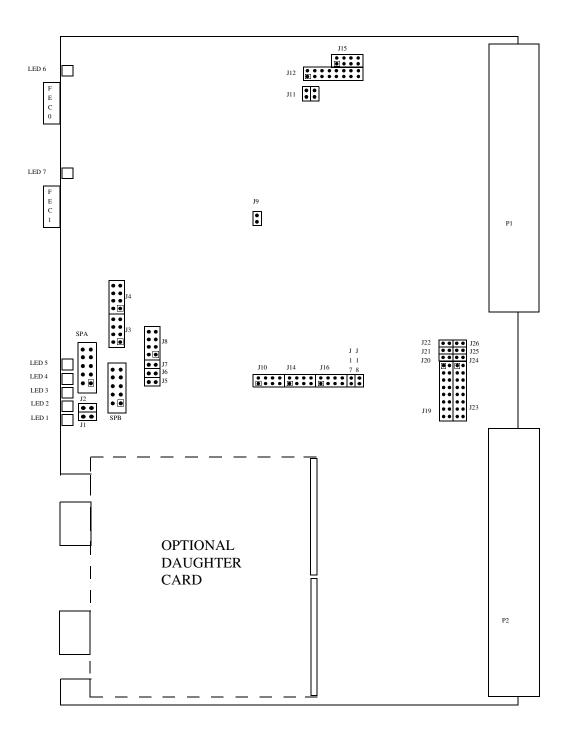

| Figure 2-2. | Single Channel AUI or 10BaseT Motherboard Layout (PB004221-001) | <br>10  |

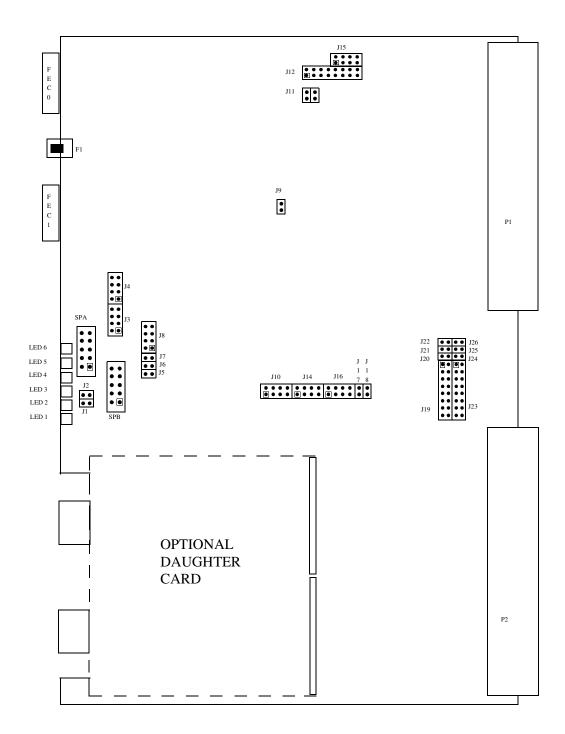

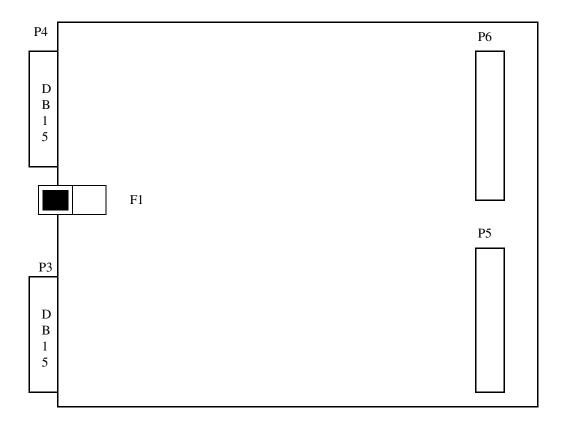

| Figure 2-3. | AUI Condor Motherboard Layout (PB04221-000)                     | <br>11  |

| Figure 2-4. | 10BaseT Condor Motherboard Layout (PB04221-001)                 | <br>12  |

| Figure 2-5. | AUI Condor Motherboard Layout (PB04221-001)                     | <br>13  |

| Figure 2-6. | Ethernet Single Channel AUI/10BaseT Daughter Card               | <br>48  |

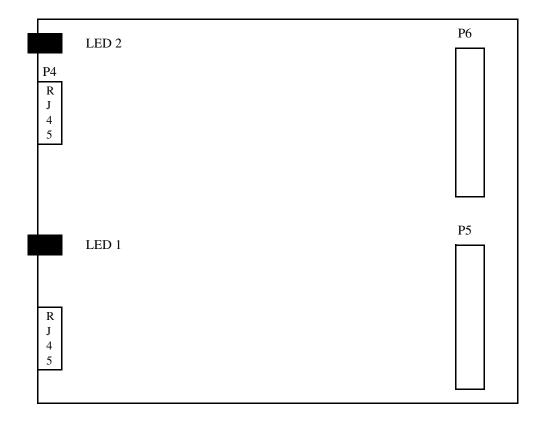

| Figure 2-7. | Dual Channel 10BaseT Ethernet Daughter Card                     | <br>49  |

| Figure 2-8. | Ethernet Dual Channel AUI Daughter Card                         | <br>50  |

# LIST OF TABLES

| Table 2-1.  | Condor Products                                  |

|-------------|--------------------------------------------------|

| Table 2-2.  | 4221 Condor LEDs                                 |

| Table 2-3.  | Board Status Diagnostics Used In POST Mode       |

| Table 2-4.  | Run Mode LED Matrix                              |

| Table 2-5.  | VME Bus Grant Settings                           |

| Table 2-6.  | Secondary Short I/O                              |

| Table 2-7.  | Primary Short I/O Size                           |

| Table 2-8.  | Primary Base Address For 2K Short I/O            |

| Table 2-9.  | Primary Base Address For 1K Short I/O            |

| Table 2-11. | Primary Base Address For 256 Byte Short I/O      |

| Table 2-12. | Secondary Base Address For 2K Short I/O          |

| Table 2-13. | Secondary Base Address For 1K Short I/O          |

| Table 2-14. | Secondary Base Address For 512 Byte Short I/O    |

| Table 2-16. | Ethernet Single Channel Daughter Card LEDs       |

| Table 2-17. | Dual Channel 10BaseT Ethernet Daughter Card LEDs |

| Table 2-18. | Ethernet Dual Channel AUI Daughter Card LEDs     |

| Table 2-19. | Ethernet Cable Options                           |

| Table 3-1.  | MACSI Memory Map                                 |

| Table 3-2.  | Master Control Status Block                      |

| Table 3-3.  | Master Status Register                           |

| Table 3-4.  | Master Control Register                          |

| Table 3-5.  | Onboard Command Queue Entry                      |

| Table 3-6.  | Queue Entry Control Register                     |

| Table 3-7.  | Offboard Command Queue Entry                     |

| Table 3-8.  | Command Response Block                           |

| Table 3-9.  | Command Response Block                           |

| Table 3-10. | Multiple Completed Returned IOPB Structure       |

| Table 3-11. | Configuration Status Block                       |

| Table 3-12. | 4207 Eagle Controller Statistics Block           |

| Table 3-13. | IOPB Commands                                    |

| Table 3-14. | Common IOPB Structures                           |

| Table 3-15. | Command Options                                  |

| Table 3-16. | DMA Transfer Control Word                        |

| Table 3-17. | Memory Type                                      |

| Table 3-18. | Transfer Type                                    |

| Table 3-19. | Initialize Controller                            |

| Table 3-20. | Controller Initialization Block                  |

| Table 3-21. | Special Network Options                          |

| Table 3-22. | MAC Control / Status                             |

| Table 3-23. | Command Options                                  |

| Table 3-24. | MAC Status / Control                             |

| Table 3-25. | Intel 82596 Transmit Status / Control            |

| Table 3-26. | Intel 82596 Receive Status / Control             |

| Table 3-27. | Change Default Node Address                      |

| Table 3-28. | Command Options                                  |

| Table 3-29. | Transmit                                         |

| Table 3-30. | Command Options                                  |

| Table 3-31. | Transmit - In-Line Gathers                       |

| Table 3-32. | Receive                                          |

| Table 3-33. | Command Options                                  |

| Table 3-34. | Common IOPB Structures                           |

| Table 3-35. | Control Flags                                    |

| Table 3-36. | Report Network Statistics                              | 95  |

|-------------|--------------------------------------------------------|-----|

| Table 3-37. | Command Options                                        | 96  |

| Table 3-38. | Network Statistics Block                               | 97  |

| Table C-39. | P1 Connector Signal Descriptions (All Versions)        | 102 |

| Table C-40. | P2 Connector For Motherboards Which Only Uses P2 Row B | 103 |

| Table C-41. | RJ45 (10BaseT) Connector Signals                       | 104 |

| Table C-42. | DB15 (AUI) Connector Signals                           | 105 |

| Table C-43. | Serial Connector Pinouts (SPA and SPB)                 | 106 |

| Table C-44. | Suggested RS232 Cable Pinout.                          | 106 |

## CHAPTER 1 INTRODUCTION

## **Intended Audience**

Interphase wrote this manual for its customers. It is intended for a highly technical audience, specifically, users who need to write their own software drivers.

Readers are assumed to have extensive knowledge of the following:

- The C programming language, including experience writing and installing interface software (drivers).

- The operating system of the host computer.

- Ethernet specifications.

- VME specifications.

## **Scope Of Manual**

The manual organization allows the user to focus on specific areas of interest, without giving more information than needed.

Specifically, this manual contains guidelines on:

- Installing the V/Ethernet 4221 Condor.

- Programming the V/Ethernet 4221 Condor, single through four port operation.

- Determining the cause of any error messages generated by the board.

## References

- VMEbus Specification, Revision C

- VMEbus Revision D, Draft 3.02, October 8, 1990

- IEEE 802.3 CSMA/CD, 1985

- Supplements to IEEE 802.3 CSMA/CD Local Area Network, 1988 through 1993

- 32 Bit Local Area Network (LAN) Component User's Manual, Intel, 1992, Order No. 296853-001

## **Conventions**

This section details many of the writing conventions used throughout the manual. In addition, it gives many of the technical conventions.

- The V/Ethernet 4221 Condor will be referred to by the name *Condor* or referenced as the *controller*.

- Byte represents 8 bits; word represents 16 bits (2 bytes); and longword represents 32 bits (2 words, 4 bytes).

- Binary (single bit) data is represented as either 1 or 0.

- To represent hexadecimal numbers, the manual adopts the C language notation. Decimal numbers are shown as decimal digits. For example:

```

0x29 = 29 \text{ hex}

41 = 41 decimal

```

- Used in the context of a single bit of data, the term set means that the bit is a one ("1").

- Similarly, the term cleared means that the bit is a zero ("0").

- In many cases, bits, bytes, and words are marked RESERVED. If the value of the reserved bit, byte, or word is sent to the controller by the host, the value must be cleared to 0.

- If the reserved value is returned by the controller, it is reserved for future use by Interphase. The user should not rely on these values to be consistent through different revisions of the product.

## **General Description**

The Condor is the second-generation multi-channel multi-function I/O Host Bus Adapter (HBA) for the VMEbus in the Cougar product line. The board is designed to maintain scalable performance and cost. The Condor architecture can be implemented with up to four Front End Channels (FECs). The FECs interface directly to a local bus, which contains a large memory buffer and a VMEbus DMA engine. This board also contains a CPU core with its own memory area and host bus interface.

#### **Features**

The basic functions and features supported by the Condor are as follows:

- Dual Ethernet Channel (10baseT or AUI) on the Motherboard.

- Dual Ethernet Channel (10baseT or AUI) on the Daughter Card.

- 8-, 16-, 32- and 64-bit VMEbus Master DMA capability.

- 25 Mbytes/second master mode burst/sustained D32 transfer rate across the VMEbus (in some modes).

- 50 Mbytes/second master mode burst/sustained D64 transfer rate across the VMEbus (in some modes).

- Programmable VME/interrupt levels and vectors.

- 16-bit, 24-bit, and 32-bit VMEbus DMA addressing, and all addressing modifiers.

- Software programmable VMEbus priority levels.

- Two VMEbus configurable 2K byte short I/O access areas of 8-bit, 16-bit, and 32-bit Slave mode transfers.

## **Options**

Interphase Corporation offers the following Condor options:

- Dual Channel Ethernet (AUI)

- Dual Channel Ethernet (10BaseT)

- 3 Channel Ethernet (AUI or 10BaseT)

- Quad Ethernet Channel (AUI or 10BaseT)

## **Physical Description**

The Condor physically conforms to the 6U VMEbus board standard. The board requires the VMEbus +5 (+/- 5%) volt supply. The board supports two channels on the main board with the associated channel connectors and up to two channels on daughter card. The cable connectors for the channels on the daughter cards reside on the daughter cards. See Appendix A for a detailed list of the Condor's physical requirements and specifications.

## **Functional Description**

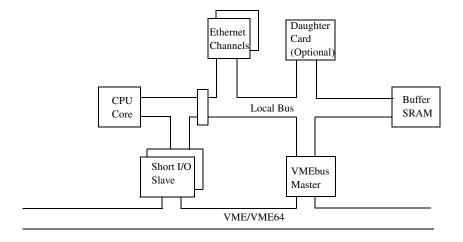

The Condor as shown in the block diagram (Figure 1-1.) consists primarily of four front-end channels, a VMEbus Master Interface, a Local Bus (LBUS), a VMEbus Short I/O (slave only) Interface, a CPU Core and a CPU/Local bus interface.

Each Ethernet Front End Channel (FEC) consists of an Ethernet controller, the associated Ethernet cable connections, front end circuitry and a small amount of Local Bus interface glue logic. The VMEbus Master Interface consists of a stand-alone VLSI DMA engine and the associated VMEbus high current driver and receiver devices. The Local Bus (LBUS) consists of the memory buffer and the associated handshake logic for the bus. The VMEbus Short I/O interface consists of the handshake and buffer logic for the host system to issue commands to the board. The CPU Core consists of a CPU with the associated memory and glue logic required to allow the CPU to control the functions of the Condor board. Finally, the CPU/Local Bus interface consists of the tri-state buffers and handshake logic required to allow the CPU to access the resources on the LBUS.

Figure 1-1. 4221 Condor Block Diagram

## **Ethernet Front End Channel (FEC)**

The 82596CA® Local Area Network (LAN) Co-processor is used as the FEC Ethernet controller. The 82596CA® communicates with the rest of the board through the LBUS. The 82596CA® has a 80486® type bus interface, which requires two PALs to convert the 80486® interface to meet the LBUS (MC68040\_ type) specification. The 82596CA® can be a master or a slave of the LBUS. As a LBUS master, the 82596CA® accesses both data and command lists for both transmits and receives commands. As a slave, the CPU has write access to four locations within the 82596CA® to establish a software reset or initialization and reset test pointers.

To complete the connections to the Ethernet cable, the 82596CA® connects to the encoder/decoder interface device (82503®) which in turn connects through analog circuitry to the cable connectors. The encoder/decoder and analog circuitry provides support for both 10BaseT and the Attachment Unit Interface (AUI).

#### **VMEbus Master Interface**

The VMEbus Master Interface consists of a VLSI DMA engine and the required high current VMEbus driver and receiver devices.

### **DMA Engine**

The DMA engine interfaces the LBUS with the VMEbus and performs the LBUS to VMEbus DMA functions. The DMA engine communicates with the rest of the board through the LBUS. The DMA engine can be a master and a slave of the LBUS. As a LBUS master, the DMA engine accesses linked list DMA commands as well as buffered data. As a LBUS slave, the DMA engine is accessed by the CPU for configuration and status information.

The DMA engine provides the VMEbus interrupter support logic, some of the internal CPU interrupts (with vectors) and the board timers.

The DMA engine also provides many functions and features which are not currently used on the Condor board. These functions include a non-DMA LBUS to VMEbus interface, VMEbus slave to LBUS interface, system controller functions, an interrupt handler and several global general purpose registers.

#### **VMEbus Drivers And Receivers**

External buffers are used to provide a more isolated and robust interface to the VMEbus. These buffers drive and receive most of the VMEbus data, address and control lines.

#### **Local Bus**

The Local Bus (LBUS) is based primarily upon a MC68040® CPU bus structure. The channels and functions connected to the LBUS must conform to the MC68040\_bus specification. This allows easy design and development of a wide variety of front ends and back ends into the controller board.

The LBUS encompasses the actual bus itself, the buffer memory and all of the logic which is not associated with any one particular channel (front end or back end) on the LBUS.

The buffer memory is configured as two SRAM banks which consists of four SRAM devices for each bank. The two banks of SRAM combined provide for 128K-, 256K-, 512K- and 1M-byte of memory.

The LBUS logic consists of an arbiter, an address decoder, a burst mode address counter, a write strobe generator, a transfer acknowledge generator, a SRAM buffer memory and any miscellaneous handshake logic required to connect the channels to the LBUS.

#### VMEbus Short I/O Interface

The VMEbus Short I/O interface allows for VMEbus host and onboard CPU communications. The host issues commands to the Condor through the Short I/O interface and the CPU issues status back to the host.

The Short I/O Interface is a Slave-only interface to the Condor and contains two independent, jumper-configurable, slave-access areas. The areas can be configured to be 256, 512-, 1K- or 2K- bytes in length.

VMEbus address lines A(15-08) and the Address Modifier lines are compared with the jumper-configurable, slave-access areas. Address Modifiers "2D" and "29" are supported for the Short I/O access.

The Short I/O Mailboxes physically reside in the CPU Core SRAM. The reset and mailbox location monitor logic resides in the VMEbus Short I/O Interface.

## **CPU Core**

The CPU (and core logic) controls and configures the rest of the Condor. Each of the commands issued to the FECs and the VMEbus DMA engine are issued by the onboard CPU.

The CPU Core consists of a MC68EC030 CPU and associated support logic. The CPU Core support logic includes the following:

- EPROM/FLASH

- Serial EPROM

- SRAM

- DUART Port

- Address Decoder

- Wait State Generator

- STERM/DSACK Generator

- Control/Status Registers

- Hardware Strobes

- Clock Generation

- Interrupt Handler

- FLASH ROM Hardware

The program for the CPU is stored in a single-byte-wide, EPROM (or FLASH) device. The EPROM can be 128K-, 256K- or 512K- bytes in size. There are two SRAM banks which consists of four SRAM devices for each bank. The two banks of SRAM combined provide for 128K-, 256K, 512K- and 1M-byte of SRAM. At board power-up, the program is copied from the EPROM (or FLASH) device to the SRAM banks. The program is then executed from the higher performance SRAM devices.

The interrupt-handler logic combines the three level interrupt from the DMA engine and the non-DMA engine-interrupt sources and outputs the three-level interrupt signals to the CPU. During CPU IACK cycles, the

interrupt handler outputs an interrupt vector number for the non-DMA engine interrupts or requests access to the LBUS for a DMA engine IACK cycles.

## **CPU/LBUS Interface**

The CPU/LBUS Interface links the CPU core with the LBUS resources. The CPU/LBUS interface converts the CPU Core bus to the LBUS. The Interface is a one-way interface which allows the CPU to act as a LBUS master. The interface does not allow other LBUS masters to access the CPU Core.

The CPU/LBUS interface is composed of address latches, data-latching transceivers, and control logic. The CPU/LBUS Interface performs write-posting and read-latching to maximize the CPU bus and the LBUS performance. The interface also performs relinquish retries, read-modify-write cycles, IACK cycles to the DMA engine, back-to-back write-write cycles and back-to-back, write-read cycles.

## CHAPTER 2 HARDWARE INSTALLATION

## Overview

Before attempting installation, read this chapter thoroughly to insure the safe installation of the Condor into your system. If you have any questions regarding installation, which are not answered in this chapter, please contact Interphase Customer Service at (214) 919-9111.

The Condor is installed into the VMEbus system using the following steps:

- Visual Inspection

- Fuse And Diagnostic LEDs

- Set Onboard Jumpers

- Set Daughter Card Jumpers

- Power Off System

- Installing the Board

- Cabling Procedure

When installing the Condor, heed the following **WARNING**:

#### WARNING

- 1. Catastrophic DAMAGE can result if improper connections are made. Therefore, those planning to connect power sources to the VMEbus for the purpose of feeding the user-defined 96 pins of P2 (Rows A and C) should FIRST CHECK to ensure that all boards installed are compatible with those connections.

- 2. Do NOT install, or apply power to, a damaged board. Failure to observe this warning could result in extensive damage to the board and/or the system.

- 3. **CAUTION!** The Condor is extremely sensitive to electrostatic discharge (ESD), and the board could be damaged if handled improperly. Interphase ships the board enclosed in a special anti-static bag. Upon receipt of the board, take the proper measures to eliminate board damage due to ESD (i.e., wear a wrist ground strap or other grounding device).

The daughter card installation procedure will vary depending on the desired configuration. Variables include:

- Single Channel AUI/10BaseT.

- Dual Ethernet AUI.

- Dual Ethernet 10BaseT.

The following table summarizes the Condor products that are available from Interphase to implement various combinations of the above functions.

Table 2-1. Condor Products

| Product                                    | Description                                                                                               |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 10BaseT Condor Motherboard (P2 Row B Only) | Provides Dual and/or Single 10BaseT Ethernet connections. This board only uses row B of the P2 connector. |

| Single Channel AUI/10BaseT Motherboard     | Provides Single AUI or 10BaseT Ethernet connections.                                                      |

| AUI Condor Motherboard                     | Provides Dual AUI Ethernet connections. This board only uses row B of the P2 Connector.                   |

| Dual AUI Ethernet Daughter Card            | Adds dual AUI connections to any of the above motherboards.                                               |

| Dual 10BaseT Ethernet Daughter Card        | Adds Dual 10BaseT connections to any of the above mother-boards.                                          |

| Single Channel AUI/10BaseT Daughter Card   | Adds a single AUI or 10BaseT channel to any of the above motherboards.                                    |

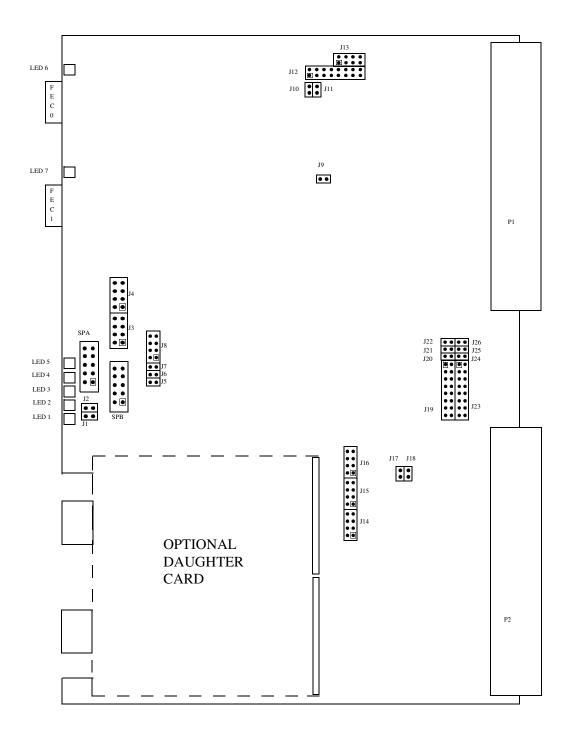

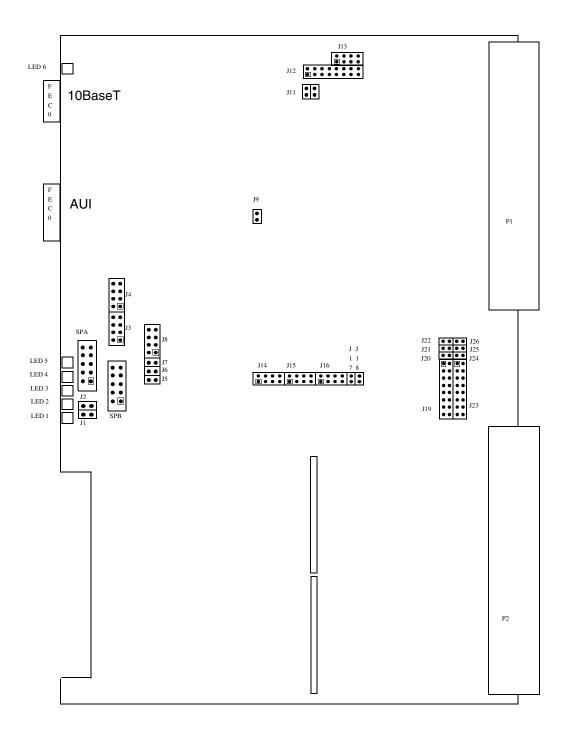

The following figures outline the board layout and jumper positions for the two different motherboard configurations:

Figure 2-1. 10BaseT Condor Motherboard Layout (PB04221-000)

Figure 2-2. Single Channel AUI or 10BaseT Motherboard Layout (PB004221-001)

Figure 2-3. AUI Condor Motherboard Layout (PB04221-000)

Figure 2-4. 10BaseT Condor Motherboard Layout (PB04221-001)

Figure 2-5. AUI Condor Motherboard Layout (PB04221-001)

## **4221 Condor Hardware Installation Procedures**

For proper installation of the Condor, it is imperative that you use the following procedures.

### **Step 1. Visual Inspection**

Before attempting the installation of this board, make sure you are wearing an anti-static or grounding device. Remove the Condor board from the anti-static bag, and visually inspect it to ensure no damage has occurred during shipment. A visual inspection usually is sufficient, since each board is thoroughly checked at Interphase just prior to shipment.

If the board is undamaged and all parts are accounted for, proceed with the installation.

## **Step 2. Fuse And Diagnostic LEDs**

The following discusses the fuse, diagnostic LEDs, and board status LEDs.

#### **Fuse**

The AUI version of the Condor has a 1.5A fuse (F1) used to protect the +12 volts when provided by the Condor. Its part number is LITTLEFUSE 273-01.5. To determine the location of the fuse on the board, refer to the appropriate board layout.

## **Diagnostic LEDs**

The Condor has as many as 8 LEDs that are mounted on the component side of the motherboard. Refer to Figures 2-1 and 2-2 for illustrations that shows the location of the component side LEDs. The following table lists all LEDs and states their function and location.

Table 2-2. 4221 Condor LEDs

| Designator | Description                           | Location       |

|------------|---------------------------------------|----------------|

| LED 1      | Board Status 0 (LSB)                  | Component Side |

| LED 2      | Board Status 1                        | Component Side |

| LED 3      | Board Status 2                        | Component Side |

| LED 4      | Board Status 3 (MSB)                  | Component Side |

| LED 5      | Board OK (Red/Green) Green = Board OK | Component Side |

| LED 6      | Fused +12 Volts Status (AUI only)     | Component Side |

| LED 7      | FEC1, Link OK Status (10BaseT only)   | Component Side |

| LED 8      | FEC0, Link OK Status (10BaseT only)   | Component Side |

## **Board Status LEDs**

LEDs 1, 2, 3, and 4 are Board Status LEDs which provide the following functions:

- Power On Self Test (POST) Mode

- Monitor Mode

- Run Mode

**POST Mode:** This mode provides diagnostics for the CPU and Buffer. Refer to the following table for a list of diagnostics performed while in this mode:

Table 2-3. Board Status Diagnostics Used In POST Mode

| Hex Code | Diagnostic               | Definition  | Type of Test            |

|----------|--------------------------|-------------|-------------------------|

| 0x01     | CPU Register Test        | CPUFAIL     | CPU Core Test           |

| 0x02     | ROM Checksum             | ROMFAIL     | CPU Core Test           |

| 0x03     | Walking 1's SRAM         | STAT1FAIL   | CPU Core Test           |

| 0x04     | Walking 0's SRAM         | STAT0FAIL   | CPU Core Test           |

| 0x05     | Decrementing Longwords   | STATLFAIL   | CPU Core Test           |

| 0x06     | Word Access              | STATWFAIL   | CPU Core Test           |

| 0x07     | Byte Access              | STATBFAIL   | CPU Core Test           |

| 0x08     | Reserved                 | RESERVED    | CPU Core Test           |

| 0x09     | Walking 1's In Buffer    | BUFFERFAIL1 | Static Buffer Test      |

| 0x0A     | Walking 0's In Buffer    | BUFFERFAIL0 | Static Buffer Test      |

| 0x0B     | Decrementing Longwords   | BUFFERFAIL  | Static Buffer Test      |

| 0x0C     | Walking 1's, 0's VME DMA | VMEFAIL     | Control Register Access |

| 0x0D     | Motherboard FEC Tests    | FEC0 & 1    | Control Register Access |

| 0x0E     | Daughter Card FEC Tests  | FEC2 & 3    | Control Register Access |

**Monitor Mode:** In this mode, LEDs will sequentially flicker when Serial Port A is active and the onboard monitor is controlling the Condor.

**Run Mode:** When in this mode, the Condor is accepting commands from the host. Refer to the following table for a list of LED definitions while in this mode:

Table 2-4. Run Mode LED Matrix

| LED1 | LED2 | LED3 | LED4 | Function                     |

|------|------|------|------|------------------------------|

| ON   | OFF  | OFF  | OFF  | 1-4 Commands On Board        |

| ON   | ON   | OFF  | OFF  | 5-16 Commands On Board       |

| ON   | ON   | ON   | OFF  | 17-64 Commands On Board      |

| ON   | ON   | ON   | ON   | 65 or More Commands On Board |

## **Step 3. Set Onboard Motherboard Jumpers**

Set all onboard jumpers so that the Condor is properly configured for operation within your system. The board layout as illustrated in figure 2-1 shows the location of the jumpers.

## **Motherboard Jumper Settings**

The following are jumpers and the default settings used on the Condor motherboard. IN refers to the jumper being installed across the pins indicated, OUT indicates the jumper is removed.

#### **CAUTION!**

Jumpers J1 through J4, J6 through J8, J10 and J11 are used for manufacturing options. If populated, they are configured to factory default settings. These jumpers must not be altered.

#### J5 FLASH0

IN: FLASH logic enabled. OUT: FLASH logic disabled.

## **J9 +12 VOLTS Flash Programming Protect:**

IN: +12 Volt power connected to EPROM socket.

OUT: +12 Volt power disconnected from EPROM socket.

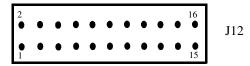

## J12 VME Bus Grant:

Pins 1 - 12 Reserved

Pins 13 - 16 VME Bus Grant:

Table 2-5. VME Bus Grant Settings

| BUS GRANT | PIN#  |       |  |  |  |  |

|-----------|-------|-------|--|--|--|--|

| DUS GRANT | 13-14 | 15-16 |  |  |  |  |

| 0         | IN    | IN    |  |  |  |  |

| 1         | IN    | OUT   |  |  |  |  |

| 2         | OUT   | IN    |  |  |  |  |

| *3        | *OUT  | *OUT  |  |  |  |  |

<sup>\* =</sup> Factory Default

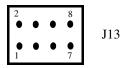

## J13 Firmware Option Jumpers:

(Pins 1-2) Reserved

(Pins 3-4) Memory Test Enable IN = Disable OUT = Enable (Pins 5-6) Console Message Disable

IN = Disable OUT = Enable

(Pins 7-8) GDB Enable Point

IN = GDB Initialized On Exit OUT = GDB Initialized On Reset

## J14 Firmware Option Jumpers:

$\begin{bmatrix} 2 & & & 8 \\ \bullet & \bullet & \bullet & \bullet \\ 1 & & & 7 \end{bmatrix}$

(PB04221-000)

(PB04221-001)

(Pins 1-2) 16 Bit Block Enable (default = OUT)

IN = 16 bit Block Mode Disabled OUT = 16 bit Block Mode Enabled

(Pins 3-4) Sysfail (default = OUT)

IN = Clear Sysfail after passing diagnostics OUT = Clear Sysfail before running Power-Up Diagnostics

(Pins 5-6) Reserved

(Pins 7-8) GDB Debugger Enable (default = OUT)

IN = Debugger Enabled OUT = Debugger Disabled

## J15 Firmware Option Jumpers / Secondary Short I/O Size:

J15

(PB04221-000)

(PB04221-001)

(Pins 1-2) Load Firmware (default = OUT)

IN = Load firmware from on-board buffer OUT = Load firmware from EPROM

(Pins 3-4) On Board Monitor Enable (default = OUT)

IN = Stop in monitor after loading firmware

OUT = Normal Run Mode

Table 2-6. Secondary Short I/O

| J15 PINS |     | SIZE (Bytes)                           |

|----------|-----|----------------------------------------|

| 5-6      | 7-8 |                                        |

| OUT      | OUT | 256 bytes of Secondary Short I/O space |

| OUT      | IN  | 512 bytes of Secondary Short I/O space |

| IN       | OUT | 1K bytes of Secondary Short I/O space  |

| *IN      | *IN | 2K bytes of Secondary Short I/O space* |

<sup>\*</sup> Factory Default

## J16 Primary Short I/O Size / Reset Enable:

Table 2-7. Primary Short I/O Size

| J16 PINS |     | SIZE (Bytes)                         |

|----------|-----|--------------------------------------|

| 1-2      | 3-4 |                                      |

| OUT      | OUT | 256 bytes of Primary Short I/O space |

| OUT      | IN  | 512 bytes of Primary Short I/O space |

| IN       | OUT | 1K bytes of Primary Short I/O space  |

| *IN      | *IN | 2K bytes of Primary Short I/O space* |

<sup>\*</sup> Factory Default

(Pins 5-6) Secondary Master Control Register (MCR) Reset Enable (default = OUT)

IN = Reset Enable

OUT = Reset Disable

(Pins 7-8) Primary Master Control Register (MCR) Reset Enable (default = IN)

IN = Reset Enabled

OUT = Reset Disabled

## J17 Secondary Channel Address Modifiers:

J17

IN = Secondary Channel Address Modifiers 29 or 2D. OUT = Secondary Channel Address Modifier 2D only.

## J18 Primary Channel Address Modifiers:

IN = Primary Channel Address Modifiers 29 or 2D OUT = Primary Channel Address Modifier 2D only

## J19, J20, J21 & J22 Primary Short I/O Base Address:

Refer to the following tables when setting Primary Short I/O Base Addresses for the following:

- Primary Short I/O For 2K Base Address

- Primary Short I/O For 1K Base Address

- Primary Short I/O For 512 Bytes Base Address

- Primary Short I/O For 256 Bytes Base Address

#### NOTE:

The normal 4221 configuration is with the Primary Short I/O space disabled. To disable the Primary Short I/O, set pins 15-16 of Jumper J19 to 0 (IN), and all other pins to F (OUT).

Table 2-8. Primary Base Address For 2K Short I/O

| ADDRESS | J19 PIN SETTINGS |       |       |      |     |     |     |     | J20, J21, J22 PIN SETTINGS |     |     |  |

|---------|------------------|-------|-------|------|-----|-----|-----|-----|----------------------------|-----|-----|--|

|         | 15-16            | 13-14 | 11-12 | 9-10 | 7-8 | 5-6 | 3-4 | 1-2 | J20                        | J21 | J22 |  |

| 0000    | F                | F     | F     | 0    | 0   | 0   | 0   | 0   | F                          | F   | F   |  |

| 0800    | F                | F     | F     | F    | 0   | 0   | 0   | 0   | F                          | F   | F   |  |

| 1000    | F                | F     | F     | 0    | F   | 0   | 0   | 0   | F                          | F   | F   |  |

| 1800    | F                | F     | F     | F    | F   | 0   | 0   | 0   | F                          | F   | F   |  |

| 2000    | F                | F     | F     | 0    | 0   | F   | 0   | 0   | F                          | F   | F   |  |

| 2800    | F                | F     | F     | F    | 0   | F   | 0   | 0   | F                          | F   | F   |  |

| 3000    | F                | F     | F     | 0    | F   | F   | 0   | 0   | F                          | F   | F   |  |

| 3800    | F                | F     | F     | F    | F   | F   | 0   | 0   | F                          | F   | F   |  |

| 4000    | F                | F     | F     | 0    | 0   | 0   | F   | 0   | F                          | F   | F   |  |

| 4800    | F                | F     | F     | F    | 0   | 0   | F   | 0   | F                          | F   | F   |  |

| 5000    | F                | F     | F     | 0    | F   | 0   | F   | 0   | F                          | F   | F   |  |

| 5800    | F                | F     | F     | F    | F   | 0   | F   | 0   | F                          | F   | F   |  |

| 6000    | F                | F     | F     | 0    | 0   | F   | F   | 0   | F                          | F   | F   |  |

| 6800    | F                | F     | F     | F    | 0   | F   | F   | 0   | F                          | F   | F   |  |

| 7000    | F                | F     | F     | 0    | F   | F   | F   | 0   | F                          | F   | F   |  |

| 7800    | F                | F     | F     | F    | F   | F   | F   | 0   | F                          | F   | F   |  |

| 8000    | F                | F     | F     | 0    | 0   | 0   | 0   | F   | F                          | F   | F   |  |

| 8800    | F                | F     | F     | F    | 0   | 0   | 0   | F   | F                          | F   | F   |  |

| 9000    | F                | F     | F     | 0    | F   | 0   | 0   | F   | F                          | F   | F   |  |

| 9800    | F                | F     | F     | F    | F   | 0   | 0   | F   | F                          | F   | F   |  |

| A000    | F                | F     | F     | 0    | 0   | F   | 0   | F   | F                          | F   | F   |  |

| A800    | F                | F     | F     | F    | 0   | F   | 0   | F   | F                          | F   | F   |  |

| B000    | F                | F     | F     | 0    | F   | F   | 0   | F   | F                          | F   | F   |  |

| B800    | F                | F     | F     | F    | F   | F   | 0   | F   | F                          | F   | F   |  |

| C000    | F                | F     | F     | 0    | 0   | 0   | F   | F   | F                          | F   | F   |  |

| C800    | F                | F     | F     | F    | 0   | 0   | F   | F   | F                          | F   | F   |  |

| D000    | F                | F     | F     | 0    | F   | 0   | F   | F   | F                          | F   | F   |  |

| D800    | F                | F     | F     | F    | F   | 0   | F   | F   | F                          | F   | F   |  |

| E000    | F                | F     | F     | 0    | 0   | F   | F   | F   | F                          | F   | F   |  |

| E800    | F                | F     | F     | F    | 0   | F   | F   | F   | F                          | F   | F   |  |

| F000    | F                | F     | F     | 0    | F   | F   | F   | F   | F                          | F   | F   |  |

| F800    | F                | F     | F     | F    | F   | F   | F   | F   | F                          | F   | F   |  |

**NOTE**: 0 = IN (Logical 0), F = OUT (Logical 1)

Table 2-9. Primary Base Address For 1K Short I/O

| ADDRESS | J19 PIN SETTINGS |       |       |      |     |     |     | J20, J21, J22 PIN SET |     |     | ETTINGS |

|---------|------------------|-------|-------|------|-----|-----|-----|-----------------------|-----|-----|---------|

|         | 15-16            | 13-14 | 11-12 | 9-10 | 7-8 | 5-6 | 3-4 | 1-2                   | J20 | J21 | J22     |

| 8000    | F                | F     | 0     | 0    | 0   | 0   | 0   | F                     | F   | F   | 0       |

| 8400    | F                | F     | F     | 0    | 0   | 0   | 0   | F                     | F   | F   | 0       |

| 8800    | F                | F     | 0     | F    | 0   | 0   | 0   | F                     | F   | F   | 0       |

| 8C00    | F                | F     | F     | F    | 0   | 0   | 0   | F                     | F   | F   | 0       |

| 9000    | F                | F     | 0     | 0    | F   | 0   | 0   | F                     | F   | F   | 0       |

| 9400    | F                | F     | F     | 0    | F   | 0   | 0   | F                     | F   | F   | 0       |

| 9800    | F                | F     | 0     | F    | F   | 0   | 0   | F                     | F   | F   | 0       |

| 9C00    | F                | F     | F     | F    | F   | 0   | 0   | F                     | F   | F   | 0       |

| A000    | F                | F     | 0     | 0    | 0   | F   | 0   | F                     | F   | F   | 0       |

| A400    | F                | F     | F     | 0    | 0   | F   | 0   | F                     | F   | F   | 0       |

| A800    | F                | F     | 0     | F    | 0   | F   | 0   | F                     | F   | F   | 0       |

| AC00    | F                | F     | F     | F    | 0   | F   | 0   | F                     | F   | F   | 0       |

| B000    | F                | F     | 0     | 0    | F   | F   | 0   | F                     | F   | F   | 0       |

| B400    | F                | F     | F     | 0    | F   | F   | 0   | F                     | F   | F   | 0       |

| B800    | F                | F     | 0     | F    | F   | F   | 0   | F                     | F   | F   | 0       |

| BC00    | F                | F     | F     | F    | F   | F   | 0   | F                     | F   | F   | 0       |

| C000    | F                | F     | 0     | 0    | 0   | 0   | F   | F                     | F   | F   | 0       |

| C400    | F                | F     | F     | 0    | 0   | 0   | F   | F                     | F   | F   | 0       |

| C800    | F                | F     | 0     | F    | 0   | 0   | F   | F                     | F   | F   | 0       |

| CC00    | F                | F     | F     | F    | 0   | 0   | F   | F                     | F   | F   | 0       |

| D000    | F                | F     | 0     | 0    | F   | 0   | F   | F                     | F   | F   | 0       |

| D400    | F                | F     | F     | 0    | F   | 0   | F   | F                     | F   | F   | 0       |

| D800    | F                | F     | 0     | F    | F   | 0   | F   | F                     | F   | F   | 0       |

| DC00    | F                | F     | F     | F    | F   | 0   | F   | F                     | F   | F   | 0       |

| E000    | F                | F     | 0     | 0    | 0   | F   | F   | F                     | F   | F   | 0       |

| E400    | F                | F     | F     | 0    | 0   | F   | F   | F                     | F   | F   | 0       |

| E800    | F                | F     | 0     | F    | 0   | F   | F   | F                     | F   | F   | 0       |

| EC00    | F                | F     | F     | F    | 0   | F   | F   | F                     | F   | F   | 0       |

| F000    | F                | F     | 0     | 0    | F   | F   | F   | F                     | F   | F   | 0       |

| F400    | F                | F     | F     | 0    | F   | F   | F   | F                     | F   | F   | 0       |

| F800    | F                | F     | 0     | F    | F   | F   | F   | F                     | F   | F   | 0       |

| FC00    | F                | F     | F     | F    | F   | F   | F   | F                     | F   | F   | 0       |

**NOTE:** 0 = IN (Logical 0), F = OUT (Logical 1)

Table 2-10. Primary Base Address For 512 Byte Short I/O

| ADDRESS |       |       |       | J19 PIN S | ETTING | S   |     |     | J20, J21, | J22 PIN SI | ETTINGS |

|---------|-------|-------|-------|-----------|--------|-----|-----|-----|-----------|------------|---------|

|         | 15-16 | 13-14 | 11-12 | 9-10      | 7-8    | 5-6 | 3-4 | 1-2 | J20       | J21        | J22     |

| C000    | F     | 0     | 0     | 0         | 0      | 0   | F   | F   | F         | 0          | 0       |

| C200    | F     | F     | 0     | 0         | 0      | 0   | F   | F   | F         | 0          | 0       |

| C400    | F     | 0     | F     | 0         | 0      | 0   | F   | F   | F         | 0          | 0       |

| C600    | F     | F     | F     | 0         | 0      | 0   | F   | F   | F         | 0          | 0       |

| C800    | F     | 0     | 0     | F         | 0      | 0   | F   | F   | F         | 0          | 0       |

| CA00    | F     | F     | 0     | F         | 0      | 0   | F   | F   | F         | 0          | 0       |

| CC00    | F     | 0     | F     | F         | 0      | 0   | F   | F   | F         | 0          | 0       |

| CE00    | F     | F     | F     | F         | 0      | 0   | F   | F   | F         | 0          | 0       |

| D000    | F     | 0     | 0     | 0         | F      | 0   | F   | F   | F         | 0          | 0       |

| D200    | F     | F     | 0     | 0         | F      | 0   | F   | F   | F         | 0          | 0       |

| D400    | F     | 0     | F     | 0         | F      | 0   | F   | F   | F         | 0          | 0       |

| D600    | F     | F     | F     | 0         | F      | 0   | F   | F   | F         | 0          | 0       |

| D800    | F     | 0     | 0     | F         | F      | 0   | F   | F   | F         | 0          | 0       |

| DA00    | F     | F     | 0     | F         | F      | 0   | F   | F   | F         | 0          | 0       |

| DC00    | F     | 0     | F     | F         | F      | 0   | F   | F   | F         | 0          | 0       |

| DE00    | F     | F     | F     | F         | F      | 0   | F   | F   | F         | 0          | 0       |

| E000    | F     | 0     | 0     | 0         | 0      | F   | F   | F   | F         | 0          | 0       |

| E200    | F     | F     | 0     | 0         | 0      | F   | F   | F   | F         | 0          | 0       |

| E400    | F     | 0     | F     | 0         | 0      | F   | F   | F   | F         | 0          | 0       |

| E600    | F     | F     | F     | 0         | 0      | F   | F   | F   | F         | 0          | 0       |

| E800    | F     | 0     | 0     | F         | 0      | F   | F   | F   | F         | 0          | 0       |

| EA00    | F     | F     | 0     | F         | 0      | F   | F   | F   | F         | 0          | 0       |

| EC00    | F     | 0     | F     | F         | 0      | F   | F   | F   | F         | 0          | 0       |

| EE00    | F     | F     | F     | F         | 0      | F   | F   | F   | F         | 0          | 0       |

| F000    | F     | 0     | 0     | 0         | F      | F   | F   | F   | F         | 0          | 0       |

| F200    | F     | F     | 0     | 0         | F      | F   | F   | F   | F         | 0          | 0       |

| F400    | F     | 0     | F     | 0         | F      | F   | F   | F   | F         | 0          | 0       |

| F600    | F     | F     | F     | 0         | F      | F   | F   | F   | F         | 0          | 0       |

| F800    | F     | 0     | 0     | F         | F      | F   | F   | F   | F         | 0          | 0       |

| FA00    | F     | F     | 0     | F         | F      | F   | F   | F   | F         | 0          | 0       |

| FC00    | F     | 0     | F     | F         | F      | F   | F   | F   | F         | 0          | 0       |

| FE00    | F     | F     | F     | F         | F      | F   | F   | F   | F         | 0          | 0       |

Table 2-10. Primary Base Address For 512 Byte Short I/O (Continued)

| ADDRESS |       | J19 PIN SETTINGS  15-16   13-14   11-12   9-10   7-8   5- |       |      |     |     |     |     | J20, J21, | J22 PIN SE | ETTINGS |

|---------|-------|-----------------------------------------------------------|-------|------|-----|-----|-----|-----|-----------|------------|---------|

|         | 15-16 | 13-14                                                     | 11-12 | 9-10 | 7-8 | 5-6 | 3-4 | 1-2 | J20       | J21        | J22     |

| 0000    | F     | 0                                                         | 0     | 0    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0200    | F     | F                                                         | 0     | 0    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0400    | F     | 0                                                         | F     | 0    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0600    | F     | F                                                         | F     | 0    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0800    | F     | 0                                                         | 0     | F    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0A00    | F     | F                                                         | 0     | F    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0C00    | F     | 0                                                         | F     | F    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 0E00    | F     | F                                                         | F     | F    | 0   | 0   | 0   | 0   | F         | 0          | 0       |

| 1000    | F     | 0                                                         | 0     | 0    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1200    | F     | F                                                         | 0     | 0    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1400    | F     | 0                                                         | F     | 0    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1600    | F     | F                                                         | F     | 0    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1800    | F     | 0                                                         | 0     | F    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1A00    | F     | F                                                         | 0     | F    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1C00    | F     | 0                                                         | F     | F    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 1E00    | F     | F                                                         | F     | F    | F   | 0   | 0   | 0   | F         | 0          | 0       |

| 2000    | F     | 0                                                         | 0     | 0    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2200    | F     | F                                                         | 0     | 0    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2400    | F     | 0                                                         | F     | 0    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2600    | F     | F                                                         | F     | 0    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2800    | F     | 0                                                         | 0     | F    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2A00    | F     | F                                                         | 0     | F    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2C00    | F     | 0                                                         | F     | F    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 2E00    | F     | F                                                         | F     | F    | 0   | F   | 0   | 0   | F         | 0          | 0       |

| 3000    | F     | 0                                                         | 0     | 0    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3200    | F     | F                                                         | 0     | 0    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3400    | F     | 0                                                         | F     | 0    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3600    | F     | F                                                         | F     | 0    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3800    | F     | 0                                                         | 0     | F    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3A00    | F     | F                                                         | 0     | F    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3C00    | F     | 0                                                         | F     | F    | F   | F   | 0   | 0   | F         | 0          | 0       |

| 3E00    | F     | F                                                         | F     | F    | F   | F   | 0   | 0   | F         | 0          | 0       |

Table 2-11. Primary Base Address For 256 Byte Short I/O

| ADDRESS |       |       |       | J19 PIN S | SETTING | S   |     |     | J20, J21, | J22 PIN SE | ETTINGS |

|---------|-------|-------|-------|-----------|---------|-----|-----|-----|-----------|------------|---------|

|         | 15-16 | 13-14 | 11-12 | 9-10      | 7-8     | 5-6 | 3-4 | 1-2 | J20       | J21        | J22     |

| 0000    | 0     | 0     | 0     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0100    | F     | 0     | 0     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0200    | 0     | F     | 0     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0300    | F     | F     | 0     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0400    | 0     | 0     | F     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0500    | F     | 0     | F     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0600    | 0     | F     | F     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0700    | F     | F     | F     | 0         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0800    | 0     | 0     | 0     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0900    | F     | 0     | 0     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0A00    | 0     | F     | 0     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0B00    | F     | F     | 0     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0C00    | 0     | 0     | F     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0D00    | F     | 0     | F     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0E00    | 0     | F     | F     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 0F00    | F     | F     | F     | F         | 0       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1000    | 0     | 0     | 0     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1100    | F     | 0     | 0     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1200    | 0     | F     | 0     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1300    | F     | F     | 0     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1400    | 0     | 0     | F     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1500    | F     | 0     | F     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1600    | 0     | F     | F     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1700    | F     | F     | F     | 0         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1800    | 0     | 0     | 0     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1900    | F     | 0     | 0     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1A00    | 0     | F     | 0     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1B00    | F     | F     | 0     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1C00    | 0     | 0     | F     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1D00    | F     | 0     | F     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1E00    | 0     | F     | F     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 1F00    | F     | F     | F     | F         | F       | 0   | 0   | 0   | 0         | 0          | 0       |

| 2000    | 0     | 0     | 0     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2100    | F     | 0     | 0     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2200    | 0     | F     | 0     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2300    | F     | F     | 0     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2400    | 0     | 0     | F     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2500    | F     | 0     | F     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2600    | 0     | F     | F     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2700    | F     | F     | F     | 0         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

**NOTE:** 0 = IN (Logical 0), F = OUT (Logical 1)

Table 2-11. Primary Base Address For 256 Byte Short I/O (Continued)

| ADDRESS |       |       |       | J19 PIN S | SETTING | S   |     |     | J20, J21, | J22 PIN SI | ETTINGS |

|---------|-------|-------|-------|-----------|---------|-----|-----|-----|-----------|------------|---------|

|         | 15-16 | 13-14 | 11-12 | 9-10      | 7-8     | 5-6 | 3-4 | 1-2 | J13       | J14        | J15     |

| 2800    | 0     | 0     | 0     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2900    | F     | 0     | 0     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2A00    | 0     | F     | 0     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2B00    | F     | F     | 0     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2C00    | 0     | 0     | F     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2D00    | F     | 0     | F     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2E00    | 0     | F     | F     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 2F00    | F     | F     | F     | F         | 0       | F   | 0   | 0   | 0         | 0          | 0       |

| 3000    | 0     | 0     | 0     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3100    | F     | 0     | 0     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3200    | 0     | F     | 0     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3300    | F     | F     | 0     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3400    | 0     | 0     | F     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3500    | F     | 0     | F     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3600    | 0     | F     | F     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3700    | F     | F     | F     | 0         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3800    | 0     | 0     | 0     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3900    | F     | 0     | 0     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3A00    | 0     | F     | 0     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3B00    | F     | F     | 0     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3C00    | 0     | 0     | F     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3D00    | F     | 0     | F     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3E00    | 0     | F     | F     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 3F00    | F     | F     | F     | F         | F       | F   | 0   | 0   | 0         | 0          | 0       |

| 4000    | 0     | 0     | 0     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4100    | F     | 0     | 0     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4200    | 0     | F     | 0     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4300    | F     | F     | 0     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4400    | 0     | 0     | F     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4500    | F     | 0     | F     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4600    | 0     | F     | F     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4700    | F     | F     | F     | 0         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4800    | 0     | 0     | 0     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4900    | F     | 0     | 0     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4A00    | 0     | F     | 0     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4B00    | F     | F     | 0     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4C00    | 0     | 0     | F     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4D00    | F     | 0     | F     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4E00    | 0     | F     | F     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

| 4F00    | F     | F     | F     | F         | 0       | 0   | F   | 0   | 0         | 0          | 0       |

Table 2-11. Primary Base Address For 256 Byte Short I/O (Continued)

| ADDRESS |       |       |       | J19 PIN S | SETTING | S   |     |     | J20, J21, | J22 PIN SE | ETTINGS |

|---------|-------|-------|-------|-----------|---------|-----|-----|-----|-----------|------------|---------|

|         | 15-16 | 13-14 | 11-12 | 9-10      | 7-8     | 5-6 | 3-4 | 1-2 | J20       | J21        | J22     |

| 5000    | 0     | 0     | 0     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5100    | F     | 0     | 0     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5200    | 0     | F     | 0     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5300    | F     | F     | 0     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5400    | 0     | 0     | F     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5500    | F     | 0     | F     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5600    | 0     | F     | F     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5700    | F     | F     | F     | 0         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5800    | 0     | 0     | 0     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5900    | F     | 0     | 0     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5A00    | 0     | F     | 0     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5B00    | F     | F     | 0     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5C00    | 0     | 0     | F     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5D00    | F     | 0     | F     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5E00    | 0     | F     | F     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 5F00    | F     | F     | F     | F         | F       | 0   | F   | 0   | 0         | 0          | 0       |

| 6000    | 0     | 0     | 0     | 0         | 0       | F   | F   | 0   | 0         | 0          | 0       |

| 6100    | F     | 0     | 0     | 0         | 0       | F   | F   | 0   | 0         | 0          | 0       |

| 6200    | 0     | F     | 0     | 0         | 0       | F   | F   | 0   | 0         | 0          | 0       |